4.2 KiB

#+TITLE:Étude structurelle du micro-ordinateur "Replica 1"

Le coeur du système : le 6205

- Le bus d'adressage est de 16 bits (pins

A0àA15) celui de donnée est sur 8 bits (pinD0àD7) On a donc un espace adressable de : 2^16 * 8 = 64 kiloctets. - Un microcontrolleur est un "tout en un" où la mémoire est incluse sur la puce, et ou les pins sont alors majoritairement des entrée/sorties. le 6205 est lui un microprocesseur en effet il ne dispose pas de broche entrées/sorties, et l'accès au bus peux se faire depuis l'extérieur, la mémoire n'est pas incluse sur la puce.

R1etR4sont des résistances de tirage, (pull-up) qui permet de fixer un état dominant(haute impédance) (ici0) à la place d'un état récessif (ici1)

Etude des circuits mémoires 27C64 et 62256

-

-

U3 :

27C64- Données: 8 bits (

DQ0àDQ7) - Adresses: 13 bits (

A0àA12)

- Données: 8 bits (

Soit un total de 2^13*8 = 64kbits= 8kiloctets Il s'agit de la mémoire morte (ROM) , en effet le signal d'écriture

WEn'est pas utilisé sur la puce U3.-

U4 :

62256- Données: 8 bits (

D0àD7) - Adresses: 15 bits (

A0àA14) (le pinA15est utilisé pour lechip select)

- Données: 8 bits (

Soit un total de 2^15*8 = 32 kilo-octets Il s'agit de la mémoire vive (RAM) en effet le signal d'écriture

WEest lui branché sur la puce. -

-

Étude de U4 : $\overline{\texttt{CS}}$ est branché sur

A15donc l'espace de mémoire s'étend de0000à7FFF. -

Le circuit U5 est un démultiplexeur.(3 adresses d'entrée, 8 sorties)

A15A14A13A12Y_iAdresse considérées 1 0 0 0 0 8XXX 1 0 0 1 1 9XXX 1 0 1 0 2 AXXX 1 0 1 1 3 BXXX 1 1 0 0 4 CXXX 1 1 0 1 5 DXXX 1 1 1 0 6 EXXX 1 1 1 1 7 FXXX Ce circuit permet de sélectionner des plages de 4 kilo-octets

-

Les sorties

Y6etY7déclenche l'accès mémoire sur U3 (ROM) les deux dernières plagesEXXXetFXXXsont donc réservées pour la ROM. $\overline{\texttt{CE}} = \overline{\texttt{OE}} = \overline{\texttt{Y}_6}.\overline{\texttt{Y}_7}$ - L'espace mémoire peux se représenter ainsi:

—–—–—–—–—–

| 0XXX | 8XXX | … | EXXX | FXXX |

—–—–—–—–—–

| RAM | ROM |

———–—–———–

Étude du circuit d'entré sortie U2

- Le composant U2 possède deux registre (A et B) de 8 bits chacun ,la sélection du registre à utiliser se fait par les pins

RS0etRS1 -

CS2 est relié à U5 sur la broche

Y_4donnant accès à la plageDXXXdonc U2 occupe une plage de 4 octets dans la mémoire.—–—–—–—–—–—–+0XXX 8XXX … DXXX EXXX FXXX —–—–—–—–—–—–+RAM I/O ROM ———–—–—–———–+

Extension de l'espace mémoire du système

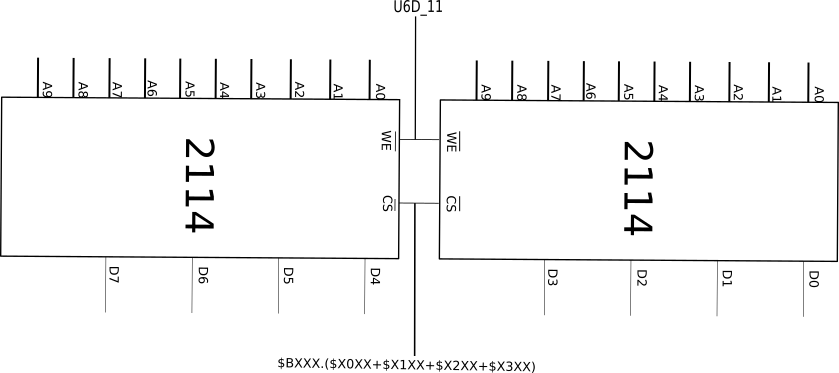

- Le circuit

2114possède une capacité mémoire de 4096 bit (512 octets) organisé en 1024 mots de 4 bits. - Pour remplir le kilo-octet de mémoire disponible (

B000àBFFF) donc 2 circuit2114sont nécessaires, pour pouvoir écrire des mots de 8 bits, sur un kilo-octet. -

et 5.

—–—–—–—–—————-—–——-—–—–0XXX … 8XXX AXXX BXXX CXXX DXXX EXXX FXXX —–—–—–—–——–——-—–——-—–—–+RAM B000 B400 I/O ROM B3FF BFFF (U2) ——–——-+2114 2114 —————–—–——–——-—–——-———–