# Master Electronique, Energie Electrique, Automatique

#### **Parcours**

Systèmes embarqués et traitement de l'information Université Paris Saclay Institut Polytechnique de Paris

# Parcours Systèmes embarqués et traitement de l'information

Partenaires : Université Paris saclay, Institut polytechnique de Paris,

Télécom Paris, ENSTA Paris, CEA/INSTN

- Objectifs : Recherche & Professionnel

- Former des étudiants à même de s'insérer dans des projets de recherche et/ou développement de réalisation de systèmes embarqués innovants

# Parcours Systèmes embarqués et traitement de l'information

Système embarqué : système électronique et informatique autonome, souvent temps réel, spécialisé dans une tâche bien précise.

# Contenu du parcours

Les innovations sur les systèmes embarqués viendront simultanément

- De la maîtrise d'un matériel de plus en plus en plus complexe (multicoeurs, manycores, GPU, DSP, FPGA) avec des contraintes de performances, consommation, sécurité, fiabilité...

- De la prise compte des contraintes logicielles (aspects temps-réel, spécifications, validation, parallélisme, etc)

- D'une bonne connaissance des applications (image, IA, robotique, signal, télécoms, etc) et de l'adaptation des algorithmes au matériel

### **Organisation du parcours**

- Basé sur des UEs de 30 heures/3 ECTS

- Stage 24 ECTS

- 12 UEs théoriques soit 36 ECTS (360 heures) :

- 2 UE TC

- 7 UE optionnelles

- Projet

- Anglais

- Initiation à la recherche ou Formation générale (gestion projet, etc)

#### Tronc commun

### 2 UEs

• T1 Architecture avancée (processeurs actuels, caches, superscalaire, VLIW,...):

A. Mérigot UPS

• T2 Systèmes Temps-Réel et Sûreté de Fonctionnement :

V. David, F. Thomas IRSN, Thales, INSTN

## **Spécialisations**

- Choix de 7 UEs optionnelles

- •Organisation des UEs en 3 spécialisations chacune de 5 Ues

- Architecture

- Systèmes et outils logiciels

- Informatique industrielle

- Traitement de données

- L'étudiant choisit une spécialisation (5 UEs)

- + 1 UE dans chacune des 2 autres spécialisations (2 UEs)

- Permet de concilier

- Spécialisation dans un domaine scientifique et technique

- Connaissances larges des différents aspects d'un système

#### Spécialisation A *Architecture*

A1 Fiabilité et sécurité des systèmes intégrés

Laurent Sauvage TP

A2 Systèmes électroniques embarqués

**Omar Hammami ENSTA**

• A3 Processeurs embarqués et architectures spécialisées

Hervé Mathias UPS

A4 Architecture et programmation parallèles

Bastien Vincke, UPS

A5 Instrumentation et interfaçage des systèmes embarqués

A. Elouardi UPS

### Spécialisation B Système et outils logiciels

- B1 Ordonnancement des systèmes temps-réel Laurent Pautet TP

- B2 Spécification et validation des systèmes embarqués Ansgar Radermacher CEA

- B3 Objets communicants Isabelle Vin UPS

- B4 Linux embarqué

Guillaume Duc TP

- B5 Programmation parallèle des GPU et des FPGA Nicolas Gac UPS

#### Spécialisation D *Traitement de données*

• D1 Vision robotique

**Emanuel Aldea UPS**

D2 Reconnaissance vocale

Claude Barras UPS

D3 Apprentissage statistique

Jean-Marc Martinez INSTN

D4 Fusion de données

Sylvie le Hégarat UPS

• D5 Identification et commande des systèmes

Sami Tliba UPS

UE additionnelle transverse

IC IA de confiance

F. Terrier CEA

• Peut remplacer une autre UE

# Organisation de l'année

- Mises à niveau TS, C++, VHDL

- S3 sept-nov 6 UEs

- 2 UEs de tronc commun

- Anglais

- Formation générale ou Initiation à la recherche

- 1 UE spécialisation

- + 1 (ou 2) autre à choisir

- S4 dec-fev 6 UEs

- 3 UEs par spécialisation

- 2 autres à choisir

- Projet (sur une des UEs de spécialisation)

- Stage Mars-Juillet

#### Remises à niveau

D'ici à fin septembre, remises à niveau dans différents thèmes :

Programmation C++

E. Aldea & N. Lerme

Traitement de signal

C. Vignat et N. Lerme

VHDL

M. Zhang

# T1: Architectures avancées Alain Mérigot (UPS)

Evolution technologique et impact sur les architectures des processeurs

Evolution des jeux d'instructions

Processeurs pipeline

Parallélisme d'instruction et processeurs superscalaire et VLIW

Hiérarchie mémoire, caches

Evaluation de performances, optimisation logicielle

18h cours, 10h TP

# T2 : Sytèmes Temps-Réel et Sûreté de Fonctionnement Vincent David (INSTN & IRSN) et Frédéric Thomas

Introduction et objectifs (problèmes clefs des systèmes temps-réel et de la sûreté de fonctionnement, problématique du logiciel, parallélisme, test et déterminisme, notion de génie logiciel)

- Synchronisation dans les systèmes asynchrones

- Verrous, problèmes liés aux architectures multicoeurs, sémaphores

- Preuves de propriétés et analyses des systèmes parallèles à partir de la modélisation en réseaux de Petri

- Introduction à la sûreté de fonctionnement des systèmes critiques

- Principe et méthode de conception des systèmes critiques cadencés par le temps, construction de systèmes parallèles déterminismes

- Principe de mise en oeuvre des systèmes critiques

21h cours, 7h TP

# A1 : UE Fiabilité et Sécurité des Systèmes Intégrés Laurent Sauvage Télécom Paris

La *fiabilité* et la *sécurité* sont deux facettes de la sûreté de fonctionnement

La fiabilité est l'aptitude d'un système à assurer la continuité de service durant un certain laps de temps

La sécurité est l'aptitude du système à préserver la confidentialité et l'intégrité des informations

Cette UE aborde ces deux notions appliquées aux circuits électroniques et dans une moindre mesure, aux systèmes embarqués

Comment analyser la sécurité ou la fiabilité d'un circuit

Comment l'améliorer (et évaluer le coût de ces améliorations)

## A2 Systèmes électroniques embarqués Omar Hammami ENSTA

Architectures de systèmes (homogènes et hétérogènes)

Technologie semiconducteur 2D et 3D

Flots de conception et de fabrication

Modélisation mathématiques et physiques de SOC

Synthèse de haut niveau

Méthodologie de conception ASIC 2D et 3D/optoelectronique.

Analyse interactions architecture/implémentation/programmation.

Projet: conception multicoeur hétérogène sur FPGA (Zynq) et ASIC (Tezzaron).

14h cours, 14h TP

# A3 Processeurs embarqués et architectures spécialisées Hervé Mathias UPS

#### Contenu

PARIS-SACLAY

- Architecture du processeur NIOS (Cours 5h) :

- différentes architectures possibles, configurations de mémoire cache, interruptions, instructions personnalisables, bus avalon pour interfacer des périphériques

- IP et périphériques embarqués (Cours 2h) :

- description de différents périphériques fournis par Altera ou University Program et mise en œuvre en association avec le processeur NIOS.

- Mini-projet (TP 23h): Implantation d'un algorithme de différentes manières sur un FPGA et comparaison des performances obtenues: implantation purement logicielle avec différentes architectures de processeur et différents types de mémoire (On Chip Ram, SRAM, SDRAM), utilisation de coprocesseurs conçus en VHDL et associés de différentes manières au NIOS (périphérique externe, périphérique sur bus Avalon,

Carte Terasic DE2-70 avec Cyclone 2

Parcours Systèmes embarqués et traitement de l'information

# A4 Architecture et programmation parallèles Joel Falcou, Alain Mérigot, Bastien Vincke Université Paris Saclay

Architectures généralistes (processeurs multi-coeurs SIMD), et accélérateurs associés (GPU et Xeon Phi)

Programmation parallèle à mémoire partagée (open-MP) ou distribuée (MPI)

Mise en œuvre du parallélisme, Cohérence de cache

Architectures pour l'embarqués: architectures légèrement parallèle (processeurs ARM, DSP Texas Instrument) et massivement parallèle (Tilera Tile64, Kalray MPPA).

Introduction aux GPU et à CUDA

Parallélisme de données. Architectures SIMD. Programmation par intrisics

19h cours, 9h TP

# A5 Instrumentation et interfaçage des systèmes embarqués Abdelhafid Elouardi UPS

# - Chaine d'acquisition de données : du capteur au calculateur

Techniques d'interfaçage capteurs, actionneurs et calculateurs. Interfaçage via une architecture programmable type FPGA. Utilisation d'une carte d'acquisition industrielle : niveau matériel et logiciel.

#### Interfaces de communications inter/intra circuits

Support physique et implantation matérielle.

Protocoles de communication synchrone/asynchrone.

Mécanisme d'optimisation d'échanges et de transmission de données.

Bus actuels: architecture, performances, commandes et protocoles d'Interfaces.

#### Interfaçage des systèmes embarqués

Caractéristiques générales et architectures matérielles des systèmes embarqués. Rapprochement des traitements auprès des capteurs/actionneurs. Méthodes de prototypage et validation.

#### Multiplexage dans les systèmes embarqués multi-capteurs

Présentation des principaux bus : CAN, LIN, FLEXRAY.

Présentation détaillée du bus CAN, du contrôleur et mise en œuvre logicielle.

Mécanisme d'optimisation d'échanges.

Etude d'un système multiplexé.

# B1 Ordonnancement et noyaux pour les systèmes embarqués temps réel Laurent Pautet Télécom ParisTech

Domaines ciblés : automobile, ferroviaire, avionique, espace

Programme: 16h CM, 10h TP, 2h TD

Théorie de l'ordonnancement mono et multi-cœurs

Noyaux temps réel et Interfaces de programmation

Environnement de programmation croisé

Noyaux et bus dans l'automobile et l'avionique

**Cours: Telecom Paris**

# B2 Modélisation de systèmes et logiciels embarqués Ansgar Radermacher CEA/INSTN

Modélisation système (SysML):

- Analyse des besoins et spécification du système.

- Modélisation de l'architecture du système.

- Modélisation du comportement.

- Modélisation d'aspects transverses.

Utilisation des modèles :

- Modélisation et analyse des propriétés temps-réel d'un système embarqué avec le profil normalisé MARTE.

- Simulation des systèmes par exécution des modèles.

Techniques avancées de l'IDM:

Définition d'un langage de modélisation spécialisé (DSML) et définition d'un générateur de code.

# B3 Objets communicants Isabelle Vin UPS

#### Télécommunications sans fil.

- Chaîne de transmission sans fil :

- codage binaire, codage source, chiffrement, codage canal (ECC), modulation, antennes usuelles dans les objets communicants.

- Canal de propagation

- phénomènes physiques, modélisation, caractéristiques du canal

- Couche PHY et techniques de traitement rencontrées :

- étalements de spectre, OFDM, MIMO, accès multiples .

Réseaux et technologies sans fil pour l'IoT.

WPAN (BLE, Zigbee, 6LowPAN, EnOcean, NFC, RFID...), LPWAN (LoRaWAN, Sigfox, etc.), réseaux mobiles de 2G à 5G.

4 séances cours, 4 séances TP

### B4 : Linux embarqué Guillaume Duc TelecomParis

#### 2 séances de cours:

Connaître les avantages et les inconvénients des solutions « Open Source »

Connaître le fonctionnement d'un système « Linux embarqué » ainsi que les principales distributions existantes.

Savoir choisir une cible adéquate et développer des pilotes pour un matériel particulier.

#### 6 séances de TP:

Installation d'un noyau « Linux embarqué » sur une « Raspberry PI 2 »

Mise en oeuvre de périphériques comme l'éthernet

Développement d'un pilote

Développement d'une application embarquée sous la forme d'un mini-projet

**Prérequis :** Langages C/C++, Systèmes UNIX/Linux (commandes et programmation)

#### **B5 Programmation parallèle des GPU et des FPGA**

#### Nicolas Gac & Abdelhafid Elouardi UPS

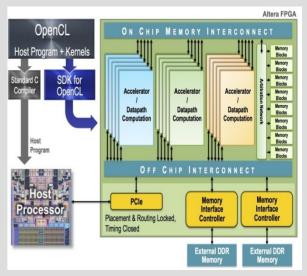

- Objectif: Parallélisation à l'aide de langage logiciel de type OpenCL pour le calcul haute performance sur systèmes embarqués hétérogènes (GPU/FPGA)

- Partie 1 (9h) : Programmation CUDA/OpenCL sur GPU embarqué

- Cours : architectures GPU Nvidia, parallélisation en CUDA/openCL, optimisation des accès mémoires (mémoire cache/mémoire locale)

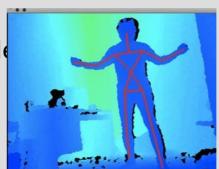

- TP: parallélisation d'algorithmes de traitement d'image sur cartes Jetson (TK1, TX, Xavier)

- Partie 2 (9h): Programmation OpenCL sur FPGA

- Cours : Synthèse de haut niveau sur FPGA

- > TP : Prise en main d'un outil de génération de code HLS

- Mini-Projet (10h) : Traitement d'un flux vidéo provenant d'une caméra embarquée

- Comparaison des performances sur les différentes architectures : temps de traitement (nb frames/s) et puissance consommée

Carte Jetson TK1 (NVIDIA)

Paradigme OpenCL sur SoC Altera

• Parcours Systèmes embarqués et traitement de l'information

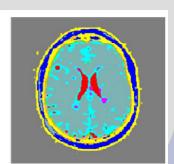

# D1 Vision robotique Emanuel Aldea, N. Lerme UPS

#### Traitements haut-niveau

Morphologie (fonctionnelle

Segmentation et optimisation

Classification (approches globales)

Détection de changement

Vision temps-réel et embarquée

Points d'intérêt

Estimation de mouvement

Couleur, texture

21h cours, 7h TP

Evaluation : contrôle continue + anlyse d'ar

Parcours Systèmes embarqués et transmisse un formation

# D2 Reconnaissance et interaction vocale Claude Barras UPS

#### Aspects théoriques

- Connaissances, modèles, algorithmes

- production et perception de la parole, phonétique

- modèles et algorithmes statistiques de décodage et traduction de la parole

Approche pluridisciplinaire : sciences cognitives, statistiques, linguistique, reconnaissance des formes, perception, psychologie, intelligence artificielle, traitement du signal...

Aspects expérimentaux et applicatifs

Thèmes de recherches présentés

- indexation multimodale et transcription enrichie de corpus audio-visuels

- interaction orale (dialogue et interaction médiatisée, détection des émotions et applications en robotique sociale)

- traduction automatique parole-parole

- Identification du locuteur

- Nombreux projets et partenaires dans un contexte technologique porteur (Apple Siri, Google Voice Search...)

Parcours Systèmes embarqués et traitement de l'information

### D3 Apprentissage Automatique et Analyse Exploratoire Jean Marc Martinez & Stéphane Gazut CEA/INSTN

Maitriser les méthodes du Machine Learning

Apprentissage supervisé, non supervisé

Réseaux de neurones : Perceptron, architectures multicouches, algorithmes d'apprentissage

Méthodes de validation : leave one out, cross validation bootstrap

Modèles à noyaux, Support Vector Machine

Classification ascendante hiérarchique, Kmeans

18h cours, 9h TPs (Scilab)

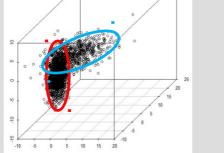

### D4 Fusion de données multicapteurs Sylvie Le Hégarat UPS

Architecture des systèmes de fusion

Méthodes probabilistes bayesiennes.

Théorie des possibilités.

Théorie des Fonctions de croyance. Théorie de l'évidence.

Étude de cas

Système de surveillance

Localisation

17h cours, 10h TP

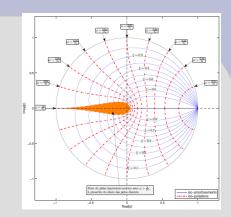

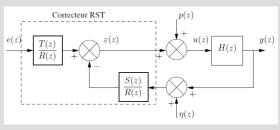

# A5 Identification & commande des systèmes :conception d'algorithmes Sami Tliba, Luca Greco UPS

#### Programme:

Commande numérique : synthèse de correcteurs numériques PID, RST

Identification: principaux algorithmes d'obtention de modèles (ARX, ARMAX, Erreur de sortie, B. & J.)

#### Objectifs:

Savoir formaliser algorithmes type récursifs en commande & identification pour implantation sur architecture de commande temps-réel

#### **Applications**:

Asservissement de systèmes : servo-mécanismes; régulation température; robotique

Estimation de paramètres : surveillance et détection de panne (monitoring); construction de modèles pour cde num.

Commande adaptative : processus évoluant au cours du temps)

# IA embarquée de confian François Terrier (CEA/INSTN)

L'IA offre de nouvelles opportunités d'enrichissement des systèmes embarqués si on arrive à en maîtriser finement l'intégration dans les environnements embarqués à la fois en termes de performance et de qualité.

Le cours est organisé en un ensemble de séminaires associés à des TP à chaque fois que des technologies accessibles le permettent.

• Enjeux de la confiance pour les IA embarquées : Panorama des questionnements et des acteurs.

#### Algorithmie, modélisation avancée :

- Compréhension et modélisation des réseaux de neurones

- Apprentissage dynamique et fédératif

#### Méthode pour la confiance :

- Explicabilité des intelligences artificielles (important pour la confiance, moins évident dans l'embarqué),

- Attaque et robustesse des réseaux de neurones (Cours

- Sécurité des réseaux de neurones et fuite de données,

#### Embarqué :

- Optimisation de l'implantation de réseaux de neurone (Cours+TP)

- micro-controleurs et architectures dédiées

#### Validation et certification :

- Validation formelle du fonctionnement de réseaux de neurones (Coul

- Analyse de risque et cadres de certification pour les applications critiques

# Anglais

Lundi après midi

1ère séance 27/09 Test de niveau

Cours lundi après midi jusqu'au 13 décembre

Passage du Toeic (à confirmer...)

## PRO et recherche

Le master est à la fois PRO et recherche

PRO: UE formation générale

(droit du travail, gestion de projet, communication)

Recherche: UE initiation à la recherche

(conférences et études d'articles)

Stage de développement en entreprise ou stage de recherche dans un laboratoire public ou privé

# Formation générale

Droit du travail

Gestion de projets

Communication

CV

Lettre de motivation

Entretien

# Initiation à la recherche

Séances de conférences sur de sujets connexes au master :

En 2020-2021 : Le calcul embarqué parallèle à TRT, temps réel probabiliste, nanocalcul, capteurs intégrés de vision, machines neuromimétiques, réalité virtuelle, réduction de la consommation des processeurs, éthique de la recherche,

Après chaque séance, présentation de 2 articles par des étudiants, discussion et critique.

# **Projet**

Projet à faire en cours d'année à partir de novembre

Deux à quatre étudiants par projet suivant les sujets

Une semaine pour finir le projet + soutenance début mars

Les projets sont liés à une UE et effectué dans un des laboratoires support du master.

Projets industriels

Les sujets seront présentés fin octobre

# Stage

De mars à septembre (durée minimale 4 mois)

Peut être dans un laboratoire de recherche ou une entreprise

Alten, Bosch, Nokia, Bull, EDF, Safran, Thales, Air liquide, Siemens, Segula, General Electric, Alsthom, Matra, valéo, Renault, etc

Start-ups: Archimej, numscale, shopline, Theraclion, Silltech, Innov+, ...

- - -

Commencer à chercher rapidement un stage Internet, répertoire du master, ...

Enseignant référent

Rapport intermédiaire après 6 semaines de stage

Rapport de stage

Soutenance début septembre

# Emploi du temps et Lieu des cours

Voir l'emploi du temps en ligne

Université Paris sud

- Bât 625

- Bât 620 (maison de l'ingénieur)

- Bât 640 (PUIO) D2 + A4, TP T1

INSTN T1, T2, B2, D3

Télécom Paris A1, B1, B4

**ENSTA A2**

# Choix des options et des UEs

Capacité d'accueil limitée des Ues (liée aux TPs)

| A1 32 | A2 32 | A3 18 | A4 20 | A5 30 |

|-------|-------|-------|-------|-------|

| B1 24 | B2 18 | B3 20 | B4 20 | B5 16 |

| D1 32 | D2 20 | D3 20 | D4 20 | D5 20 |

→ Capacité d'accueil limitée des options.

Dépend du nombre d'étudiants total

Envoi d'un formulaire de choix d'option jeudi

Formulaire de choix des UEs optionnelles **lundi**

Attention certains choix sont impossibles car des cours sont en parallèle

Permutation éventuelles ultérieurement

#### Débouchés

#### RECHERCHE

Thèse dans un des laboratoires associés au M2R : CEA, SATIE, ENSTA, Télécom Paris, INRIA, LIMSI, LRI, LSS, etc

Recherche industrielle (thèse CIFRE)

#### **PRO**

Industrie électronique, informatique, équipementiers, semiconducteurs, transport, télécom, etc

#### Validation du master

Validation des UEs : les modalités de contrôle de chaque UE sont sur le site Paris Saclay.

En général prise en compte de l'examen et des Tps.

L'UE est validée si la note est supérieure à 10

#### Le master est validé si :

- soit toutes les UEs sont validées pour chacun des semestres

- soit la moyenne du semestre est >10 et les UEs non validées sont compensables (note > 7)

Pas de redoublement en M2 (sauf cas particulier)

#### Financement de thèse

Nombreux mécanismes de financement

Ecole doctorale(s) (bourses du ministère)

Bourses d'organismes de recherche : CNRS, CEA, IFSTTAR, INRIA, ASE, etc.

Bourses CIFRE (collaboration entre organisme de recherche public et industrie)

Financement sur contrat de recherche

#### **Divers**

Préinscription puis inscription en ligne

En cas de difficultés, le mieux est d'aller au bâtiment 336.

Logement...

#### Comptes informatiques:

- indispensables pour les TPs. Incrivez vous à l'université au plus vite et validez votre compte u-psud

- Procédure particulière pour étudiants IPP

Secrétariat bât. 625, s. 220, bureau des professeurs s. 217

# QUESTIONS?