# LOW POWER TECHNIQUES OVERVIEW – FOR SOC

Master 2 – SETI | Paris-Saclay University

Farhat THABET, CEA LIST, Saclay | 14/12/2021

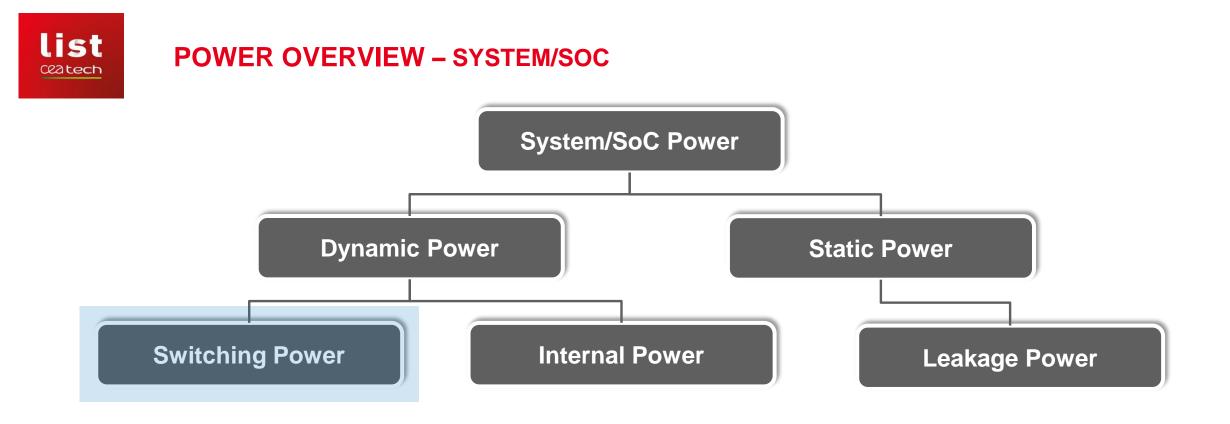

# System Power = Dynamic Power + Static Power

**Note:** Static Power part is not important compared to Dynamic Power part.

# **POWER OVERVIEW** : DYNAMIC POWER – SWITCHING PART

Power generated due to output/signal changes, thus charging and discharging the load capacitance.

Switching power dissipates mainly depend on the :

- System Clock Frequency

- Activity Switching Frequency

Switching Power Calculation depends on the three factors

- C Load Capacitance

- *f Switching Freqency*

- V Voltage

$$P_S = C * V^2 * f$$

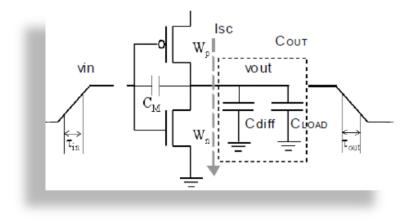

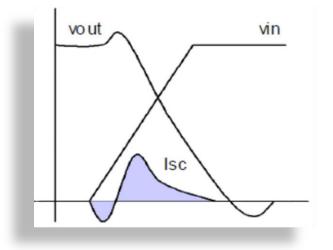

# **POWER OVERVIEW** : DYNAMIC POWER – INTERNAL PART

- Short circuit path has been created between power and ground at the transition stage

- Thus the **short circuit current** is generated

- Power dissipation due to this temporary short circuit path and the internal capacitance is Internal Power

- Depends on some factors,

- Input edge time

- Slew Rate

- Internal Capacitances

$$P_I = V * I_{SC}$$

**Dynamic power** is the sum of **switching power** and **internal power**

$$P_{D} = P_{S} + P_{I}$$

$$P_{D} = C * V^{2} * f + V * I_{SC}$$

$$P_{D} \stackrel{\sim}{=} C_{eff} * V^{2} * f_{switch}$$

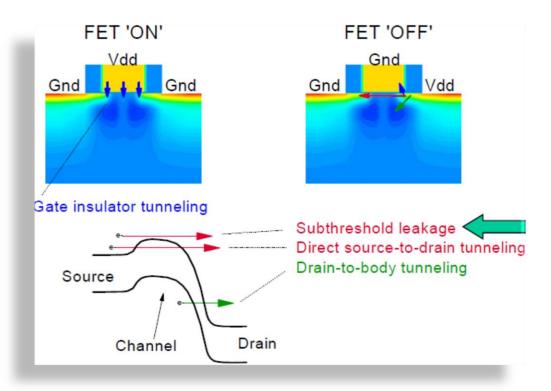

# **STATIC POWER**

- Due to non-idle characteristic of the transistor the leakages can be taken place

- **Static power** is nothing, but **leakage power**

- There are two main types of leakages and their subsidiaries

- *I*<sub>OFF</sub> Sub-threshold leakage (Drain Leakage Current)

- I<sub>D,weak</sub> Sub threshold Drain Current

- *I<sub>inv</sub> Reverse Biased Current*

- I<sub>GIDL</sub> Gate Induced Drain Leakage

- I<sub>GATE</sub> Gate Leakage Current

- I<sub>TUNNEL</sub> Gate Tunneling

- *I<sub>HC</sub>* Hot Carrier Injection

### **POWER ESTIMATION**

Mostly based on the tech libraries

Based on two major calculations

- Activity

- The number of toggles per clock cycle on the signal, averaged over many cycles

- **Probability**, and **Percentage** of the time that the signal will be high

| 0 10ns 20 30 40 | Activity | Probability |

|-----------------|----------|-------------|

|                 | 2.0      | 0.5         |

| N1              | 0.5      | 0.9         |

| N2              | 1.0      | 0.5         |

P = (time at logic 1) total time Clock cycle boundaries do not matter

- DVFS Dynamic Voltage Frequency Scaling

- DPM, Clock Gating, Power Gating

- ☐ Multi VDD, Voltage Islands

- Device Level

- Multi Threshold Devices

- Low Capacitance in device

- High k Hf based MOS

# DVFS – Dynamic Voltage Frequency Scaling

- DPM, Clock Gating, Power Gating

- Multi VDD, Voltage Islands

Device Level

- Multi Threshold Devices

- Low Capacitance in device

- High k Hf based MOS

## LOW POWER TECHNIQUES : DVFS - DYNAMIC VOLTAGE AND FREQUENCY SCALING (1/3)

DVFS is a method to provide variable amount of energy for a task by scaling the operating voltage/frequency.

Power consumption of a CMOS-based circuit is :

$\boldsymbol{P}_{\boldsymbol{D}} \doteq \boldsymbol{\alpha} \ast \boldsymbol{C}_{eff} \ast \boldsymbol{V}^2 \ast \boldsymbol{f}$

α : switching factor

C<sub>eff</sub> : effective capacitance

V : operating voltage

f : operating frequency

**Energy** required to run a task during T is :

$E = P \cdot T \propto V2$

(assuming  $V \propto f$ ,  $T \propto f-1$ )

By **lowering** CPU frequency, CPU energy can be saved.

# LOW POWER TECHNIQUES : DVFS - DYNAMIC VOLTAGE AND FREQUENCY SCALING (2/3)

- Choosing a frequency in DVFS

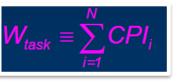

- Workload of a task, W<sub>task</sub>, is defined as the total number of CPU clock cycles required to finish the task :

N : total number of instructions in a task CPI : clock cycles per instruction

Task execution time,  $T_{task}$ , is a function of the CPU frequency,  $f^{cpu}$

• Given a deadline of D,  $f_{target}$  denotes the CPU frequency that results in  $T_{task}$  closest to D

$$f_{target} = rac{W_{task}}{D} \implies T_{task} = D$$

## list <sup>Ceatech</sup>

# LOW POWER TECHNIQUES : DVFS - DYNAMIC VOLTAGE AND FREQUENCY SCALING (3/3)

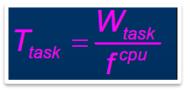

Example : a task with workload W should be completed by a deadline, D.

DVFS is an effective way of reducing the CPU energy consumption by providing "justenough" computation power.

# DVFS – Dynamic Voltage Frequency Scaling

- DPM, Clock Gating, Power Gating

- Multi VDD, Voltage Islands

- Device Level

- Multi Threshold Devices

- Low Capacitance in device

- High k Hf based MOS

#### LOW POWER TECHNIQUES : DPM, CLOCK GATING, POWER GATING (1/5)

- Clock Circuitry Power Consumption

- 15 to 45% of **Total Power**

- P (clock circuitry) ∝ Frequency

- Clock tree consume more than 50 % of dynamic power. The components of this power are:

- Power consumed by **combinatorial logic** whose values are changing on each clock edge, and

- Power consumed by flip-flops

Activity of Functional Units

A (units) < 50% in Execution Time</p>

#### list <sup>Ceatech</sup>

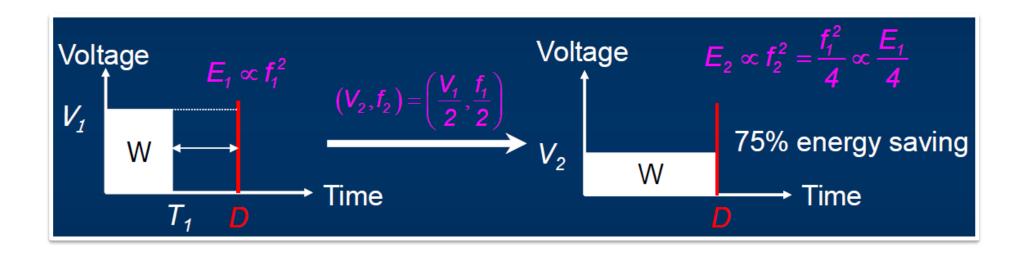

## LOW POWER TECHNIQUES : DPM, CLOCK GATING, POWER GATING (2/5)

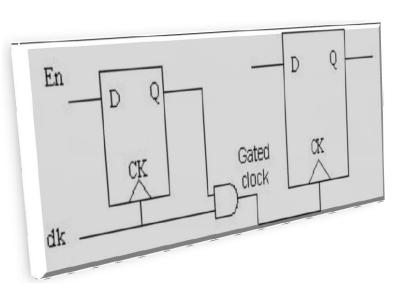

Clock Gating and Power Reduction : two types :

- a. Latch-free clock gating

- b. Latch-based clock gating

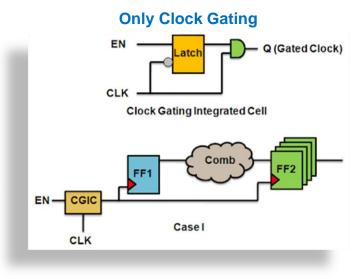

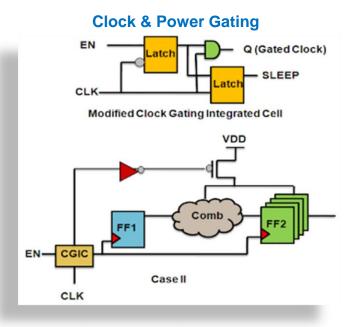

# LOW POWER TECHNIQUES : DPM, CLOCK GATING, POWER GATING (3/5)

# Clock Main Idea

- Clock Circuitry Gating (Case I)

- Shutting/Power down Unused Partitions (Case II)

# Implementation

- Creating Local Clocks

- Buffers or Flip-Flops with enable or/and Sleep signal

# Net Effects

- Reduction of Unnecessary Switching

- Reduction of Clock Circuitry

- Power Consumption Reduction

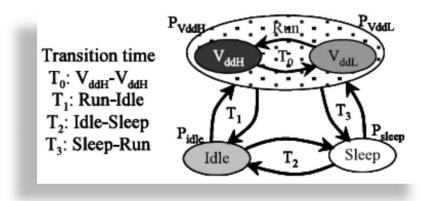

# LOW POWER TECHNIQUES : DPM, CLOCK GATING, POWER GATING (4/5)

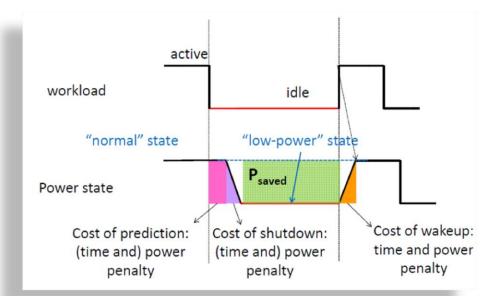

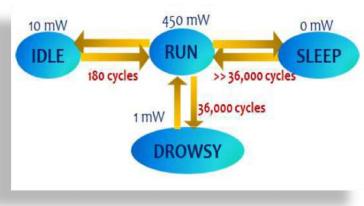

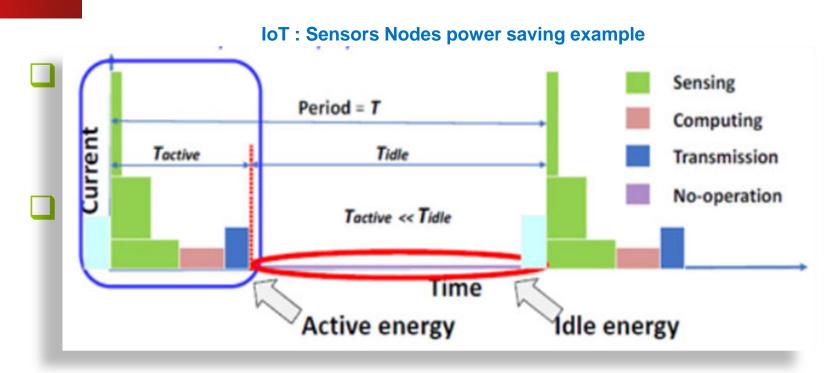

Dynamic Power Management Main Idea

- Active the good power mode of each system component

- Shutting/Idle/Sleep down unused components

Implementation

- Inactivity period prediction and/or calculation depending in workload

- Optimal power states definition and activation

# Component Effects

- Power down unused/inactive components

- Power Consumption Reduction

# LOW POWER TECHNIQUES : DPM, CLOCK GATING, POWER GATING (5/5)

**Architecture**

Component Effects

list

Ceatech

- Power down unused/inactive components

- Power Consumption Reduction

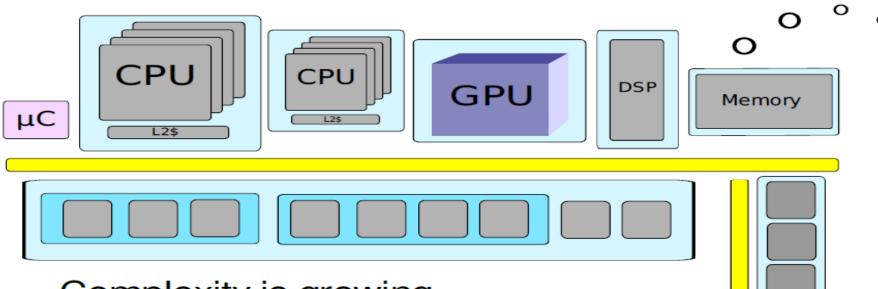

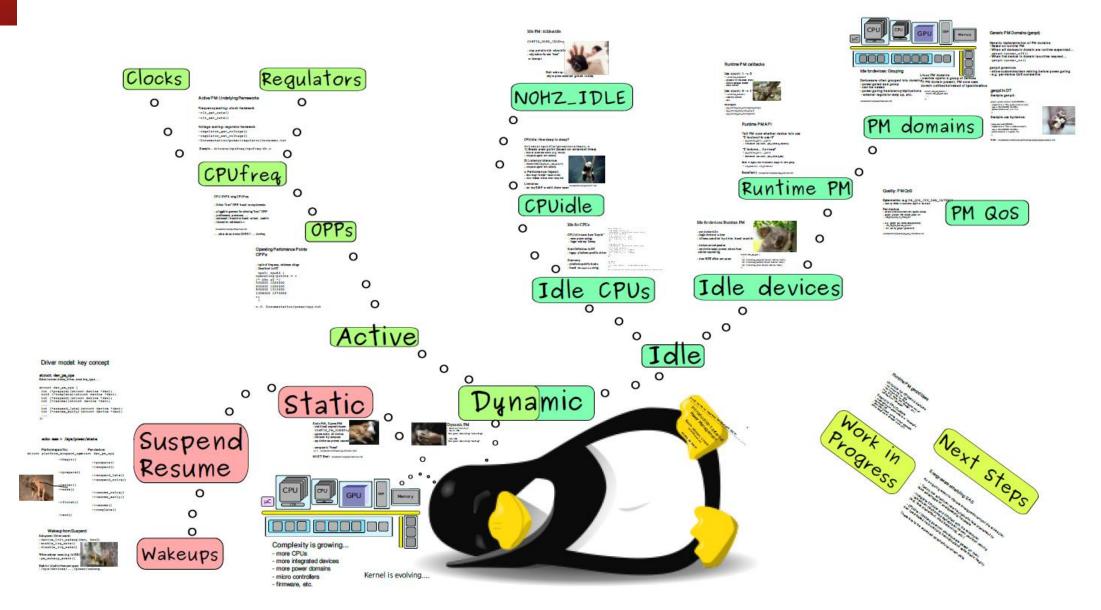

# LOW POWER TECHNIQUES : RUNTIME SUPPORT (1/2)

Complexity is growing...

- more CPUs

- more integrated devices

- more power domains

- micro controllers

- firmware, etc.

Kernel is evolving....

To support several power management techniques

#### list <sup>Ceatech</sup>

# LOW POWER TECHNIQUES : RUNTIME SUPPORT (2/2)

DVFS – Dynamic Voltage Frequency Scaling

DPM, Clock Gating, Power Gating

# ☐ Multi VDD, Voltage Islands

Device Level

- Multi Threshold Devices

- Low Capacitance in device

- High k Hf based MOS

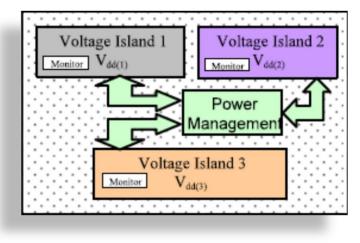

# LOW POWER TECHNIQUES : MULTI VDD, VOLTAGE ISLAND

# Multi-VDD design Main Idea

- Allows a finite number of supply voltages depending on power requirements of the system.

- Dynamic change of voltage supply depending on the workload

# Implementation

- Multi-VDD design sectors

- Advanced optimal power states definition and activation

# Component Effects

- Fine Grain Power management

- Power Consumption Reduction

#### Multiple Voltage Island Design

#### Power State Machine (PSM) with Multi-VDD

DVFS – Dynamic Voltage Frequency Scaling

- DPM, Clock Gating, Power Gating

- Multi VDD, Voltage Islands

Device Level

- Multi Threshold Devices

- Low Capacitance in device

- High k Hf based MOS

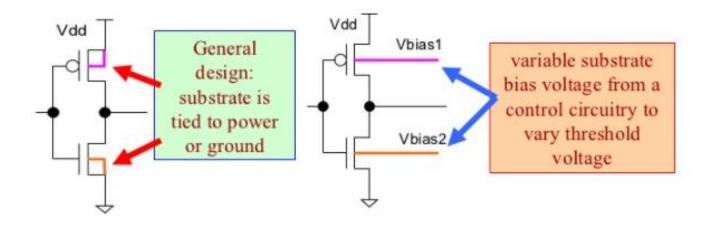

# LOW POWER TECHNIQUES : MULTI-THRESHOLD DEVICES (CMOS)

list

Ceatech

Multi-threshold is one kind of CMOS which is a deviation in the chip technology.

- It has transistor with **multiple threshold voltages** in order to optimize delay or power.

- It can achieve a lower threshold voltage, and therefore, higher performance as well as smaller standby leakage current.

- Simple threshold of making MOS with multiple threshold voltages is to apply different bias voltage to the body or substrate terminal of the transistors.

- It enables high performance and low power operation, but requires sequential circuit structures that can retain state during standby modes.

# Thank you Any Question ?

#### LOW POWER TECHNIQUES OVERVIEW - SOC DESIGN

Master 2 – SETI | Paris-Saclay University

Farhat THABET, CEA LIST, Saclay | 14/12/2021